Что такое ПЛИС простым языком для начинающих

Содержание статьи

Отличия от микроконтроллеров

Для разработчиков в микроконтроллерах доступен фиксированный набор решений и средств присущих конкретному чипу, отступить от архитектуры никаким образом не получится. Вам предоставлен набор команд, с помощью которых вы производите операции взаимодействия с окружающей средой, посредством считывания данных с цифровых и аналоговых входов и отправка сигналов исполнительным устройствам с помощью выходов.

Кроме этого вы можете производить вычисления, сохранять данные в регистрах или ПЗУ, а также оперировать данными прошитыми в память микроконтроллера. На этом в сущности и заключается назначение и особенности работы с микроконтроллерами.

Программируемые логические интегральные схемы (ПЛИС) отличаются тем, что, программируя устройство вы сами создаете архитектуру из базовых логических элементов. Таким образом вы получаете высокое быстродействию и гибкость микросхемы. Это даёт возможность, не изменяя одного чипа сделать целый ряд проектов.

Обобщённо внутреннее устройство ПЛИС можно разделить на три основных группы:

1. Массив из логических элементов (макроячеек, логических блоков).

2. Блоки входа-выхода (IO).

3. Линии связи между ними и устройство, которое управляет этими связями.

Однако такое структурирование очень обобщено, немного подробнее мы рассмотрим этот вопрос ниже.

Программируя вы соединяете элементы подобно тому как бы вы это делали, собирая из отдельных элементов устройство и соединяя их входы и выходы проводниками.

Главным отличием ПЛИС от микроконтроллеров является то, что в микроконтроллере вы не можете изменять внутренних связей между простейшими элементами, а в ПЛИС на основе прописывания связей основывается программирование и работа с ними.

Выбор микроконтроллеров происходит на основе множества критериев, таких как:

Быстродействие и тактовая частота;

Количество входов и выходов.

Другие функциональные особенности и периферии, типа поддержки линий связи и протоколов (I2C, one-wire, PWM-сигнал и прочее).

В зависимости от конкретного ПЛИС количество блоков может изменяться в широких пределах, соответственно изменяется и стоимость.

Микроконтроллер выполняет последовательно все операции, прописанные в его программе, в то время как блоки ПЛИС выполняют задачу параллельно и независимо друг от друга, поэтому сравнение этих устройств по тактовой частоте нецелесообразно. Слишком различается их принцип работы.

Виды

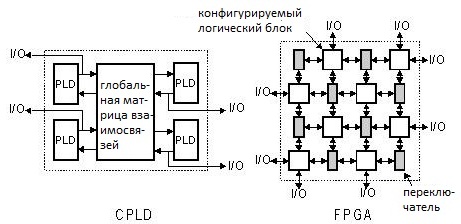

Актуальными на сегодняшний день являются два основных вида ПЛИС:

Внутренняя структура строится на матрице макроячеек или логических блоков, а количество элементов в них лежит в пределах сотен и тысяч штук. Благодаря относительной простоте стоят дешевле чем следующий вид программируемой логики. Всё это приводит к тому, что используется CPLD в основном в схемах, где нужна высокая скорость и большое число выводов, при этом выполняют несложные задачи.

Прошивка, как правило, хранится во внешней энергонезависимой памяти. Кроме простейших логических элементов в FPGA могут содержаться готовые блоки для выполнения каких-либо операций, например, блоки обработки сигнала DSP. Всё это позволяет реализовать процессор, устройства обработки сигналов и другие сложные устройства.

Интересно:

Хотя фактически наличие энергонезависимой памяти не делает программируемую логику CPLD. Это частично заблуждение. Главным отличием CPLD от FPGA является внутренняя структура.

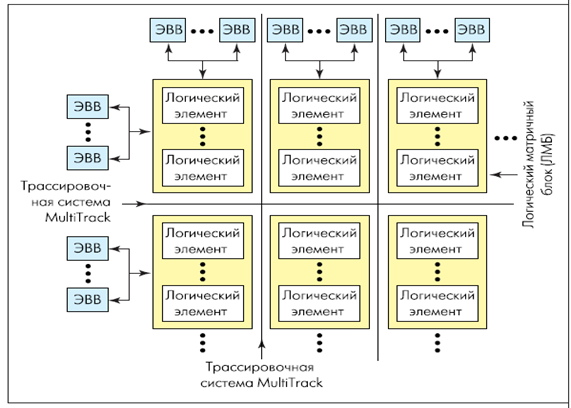

Подробнее внутреннее устройство CPLD изображено на рисунке ниже.

А примерная схема её макроячейки выглядит таким образом:

Макроячейка состоит из программируемых мультиплексоров, триггеров (одного или нескольких) и формирует группу выходных сигналов ФБ в нескольких их вариантах.

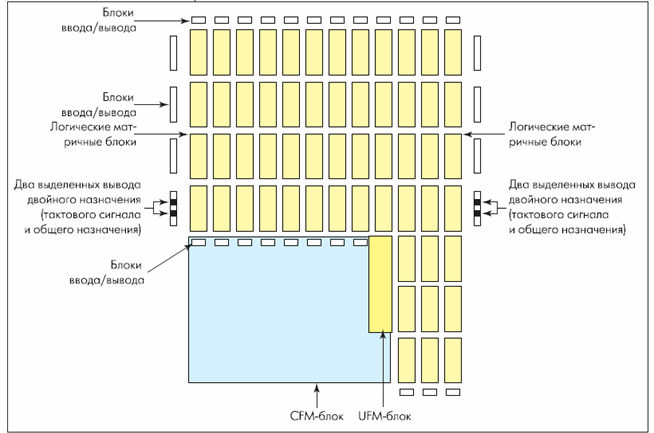

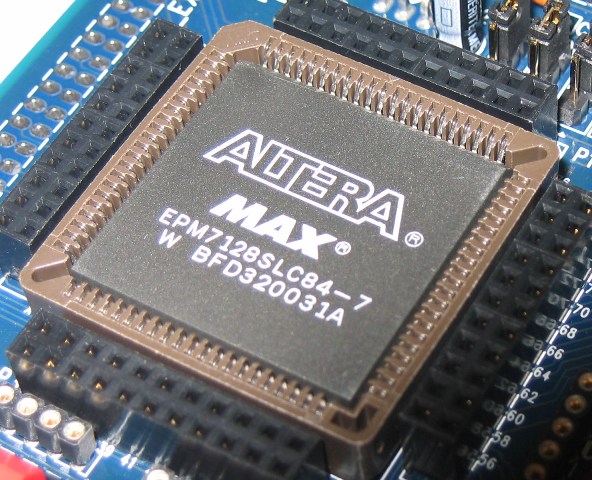

Ниже приведен еще один пример – блок-схема CPLD микросхемы семейства MAX II фирмы Altera.

И структурный план микросхем этого же семейства.

Промежуточные шины макроячейкам назначаются с помощью такого узла, как распределитель, на англ. он звучит как Logic Allocator, что изображено на схеме ниже, на ней же изображена матрица переключений (Global Routing Pool), а у выходных макроячейки (macrocells) имеют по две обратных связи.

Внешние выводы микросхемы соединяются с выходами макроячеек через еще один блок (матрицу) – ORP (Output Routing Pool), обратите внимание, что через неё же происходит соединение ВХОДНОЙ логики с GRP, что изображено на иллюстрации ниже.

В некоторых CPLD есть т.н. прямые входы (Direct Input) – они соединены со входами ячеек напрямую, что уменьшает задержки.

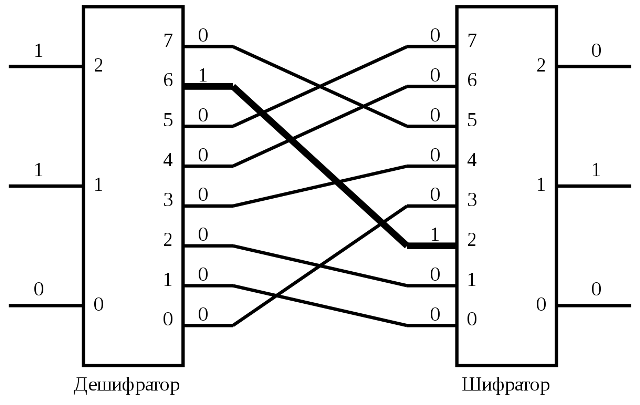

У FPGA структура имеет вид:

L – логический конфигурируемый блок;

S (substitution block) – блок подстановок, он получает на ход определенное число бит, преобразует, по определенному алгоритму, а на выходе выдаёт другое число бит. Другими словами – дешифратор, шифратор и коммутатор.

C (connection block) – блок соединений.

Научитесь разрабатывать устройства на базе микроконтроллеров и станьте инженером умных устройств с нуля: Инженер умных устройств

Программирование

Разработчикам, которые работают с ПЛИС доступно графическое программирование. То есть вы можете просто рисовать логические схемы или комбинировать код с графикой. Последнее называют модульным методом разработки, когда конкретные модули прописываются, а верхний модуль, в котором всё объединяется программируется графическим способом.

Подборка полезных статей про микроконтроллеры:

Примеры популярных производителей и серий ПЛИС

На момент написания статьи наиболее известными являются изделия двух производителей.

Altera (основана в 1983 году);

Xilinx (Основана в 1984 году).

У Altera есть несколько основных серий программируемой логики:

Сделай шаг к ПЛИС

Ты ждал знак? Вот он!

Много лет я не решался начать программировать ПЛИС, потому что это сложно, дорого и больно (как мне казалось). Но хорошо, когда есть друзья, которые помогают сделать первый шаг. И теперь я не понимаю одного — ПОЧЕМУ Я ЖДАЛ ТАК ДОЛГО?

Сейчас я помогу сделать первый шаг и тебе!

А зачем оно мне?

Ты устал постоянно читать доки по своему МК или держать кучу информации в голове. Ты все переписал на asm, но скорости все равно не хватает. Ты подключил два внешних устройства к своему МК, подключаешь третье, но у тебя кончились прерывания, перестают работать те модули, что уже работали. Ты берешь другой МК, более мощный из той же линейки, но опять мануалы, регистры флагов, биты… ад. Меняешь платформу: переходишь на другой МК и выкидываешь на помойку свои знания по прежней платформе. Что бы ты не делал — оно дается тяжело. Ты находишь популярную платформу, в которой можно легко из компонентов собирать проект, но выше аппаратных ограничений данного МК все равно не удается прыгнуть… Где-то на краешке сознания иногда проскакивает мысль, что вот на ПЛИС это бы точно заработало быстро и параллельно, что это «именно та задача, которую бы надо решать на плис», но я стар/глуп/занят/etc чтобы суметь/начать такое делать.

Хочешь наконец вздохнуть свободно? Идем дальше!

Радость от разработки на ПЛИС

У меня был тяжелый рабочий день. С одной работы я приехал на вторую работу, потом на дачу, вечером домашние дела, уроки, потом семейный просмотр кино и только в 23 часа я оказался совершенно свободен! Сказать, что я был уставший — ничего не сказать. Но в таком состоянии я сел за ноут с твердой целью: сделать генератор меандра на 440 Гц. Прошло 20 минут и я уже слышал его в наушниках. Я не верил своим ушам! Еще 15 минут мне потребовалось, чтобы сделать ШИМ и менять громкость. К тому времени плата с ПЛИС у меня была всего с неделю и до этого я пролистал всего пару книг по Verilog.

В тот вечер я понял: ВОТ ОНО! Вот та платформа, в которой я быстро и легко могу превращать свои мысли в реально работающее железо!

Почему так?

Проблема выбора

Сильно останавливают вопросы, что выбрать: Altera/Xilinx, Verilog/VHDL, какую отладочную плату взять. Но обо всем по порядку.

Производитель

Я выбрал Altera. Почему? Ну мы вот так с другом решили, хотя название Xilinx мне красивее. НО. Если ты сейчас не можешь выбрать, то я сделаю это за тебя. Тебе нужен Altera! Почему? Я не знаю. Сейчас важнее сделать шаг: сделать выбор. Я выбрал Altera и пока не пожалел.

Берем Verilog — потомучто… ну ты понял.

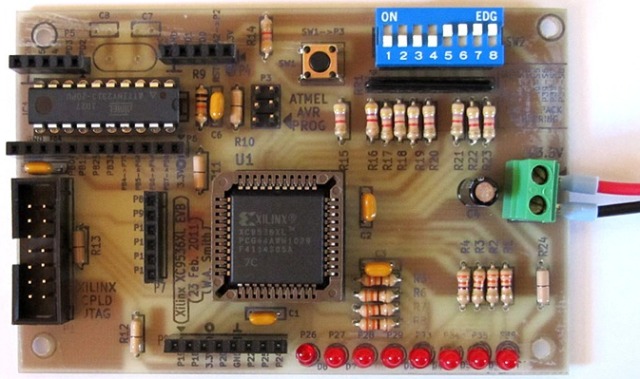

Отладочная плата

На выбор отладочной платы ушло больше всего времени. Понятно, что платы отличаются установленной микросхемой ПЛИС. А микросхемы ПЛИС отличаются друг от друга количеством элементов. Но совершенно не понятно, сколько их потребуется для твоих тестовых проектов. Поэтому большую часть времени я потратил на поиск всевозможных проектов на ПЛИС на предмет того, чтобы узнать, сколько они потребляют ресурсов ПЛИС.

В семействе Altera, за разумные деньги мы можем купить платы с CPLD MAX II на 240, 570 и 1270 элементов, либо более старшие микросхемы FPGA, которые Cyclone 1, 2, 3, 4 с количеством до 10000 и более ячеек. Как же выбрать?

Даже на базе 240 ячеек, проект Марсоход делает просто огромное количество проектов. Настоятельно рекомендую ознакомиться, чтобы иметь примерное представление о сложности проектов, которые можно уместить в 240 ячеек. С другой стороны, существуют проекты, которые полностью программируются под аппаратную копию определенного ПК, включая процессор и всю логику вокруг него (NES, Speccy, Orion, ЮТ-88, etc). Для этого уже требуется пять, десять и более тысяч ячеек. Плюс эти платы содержат дополнительные внешние устройства.

Поэтому я бы посоветовать взять что-то среднее между 240 и 10000 ячейками, с предпочтением в сторону увеличения в зависимости от доступных средств. На отладочной плате лишние ячейки это не страшно, а если их не хватит — уже ничего не поделаешь. Потом, когда устройство отлажено, станет ясно, сколько надо ячеек, купить под нужное количество, без лишнего «обвеса», дешевле и оставить в готовом устройстве.

То, чем действительно отличаются MAX от Cyclone’ов, кроме количества ячеек, это:

1) У серии MAX внутри нет PLL. На каждой отладочной плате есть генератор, как правило на 50 МГц. Основной массе проектов этого будет достаточно. Все синхронизации будут происходить путем деления 50 МГц на какое-нибудь значение. Либо, можно взять внешний генератор и подать на отдельный вход ПЛИС. А что, если потребуется частота выше 50 МГц? Мне не удалось с ходу найти генераторы выше 50 МГц. Но тут как раз на помощь и приходит PLL, который встроен в Циклоны. На нем можно умножить частоту, например, до 100 МГц.

2) В серии Cyclone встроены аппаратные блоки умножения. Их количество зависит от конкретной модели — тут как раз можно «всетаки заглянуть в инструкции», чтобы узнать сколько. Если предполагаете делать какой-то ЦОС, то они пригодятся: сэкономят ячейки, увеличат скорость. С другой стороны, если нет умножителей, их можно синтезировать, но у маленькой ПЛИС на это может не хватить ресурсов.

Во всем остальном у меня критерий «влезло/не влезло». Отладка на заведомо бОльшей, чем нужно плате, с последующей заливкой в минимально необходимую для этого.

Сколько нужно денег?

Программатор

Я считаю, что у меня нет времени, чтобы паять программаторы на рассыпухе.

300 рублей. Я свой брал на ебее, выглядит так:

Отладочная плата

Выбор широкий, в зависимости от количества денег.

Начальный уровень 350 — 550 рублей. Это платы на MAX II (240 или 570 ячеек). Могут подойти для начального ознакомления и дальнейшего пристройства в конечные устройства. На плате есть генератор, пара кнопок, пара светодиодов, остальные 80 выводов на свое усмотрение.

Блок питания

Обязательно должен быть, но не всегда идет в комплекте. Потребуется БП на 5 вольт и ток 2А.

Средний уровень от 900 до 1500 рублей. Это платы Cyclone 1, 2, 3, 4 отличающиеся в основном количеством ячеек.

Маркируются примерно так:

EP2C5T144 — Cyclone 2 примерно 5к ячеек

EP4CE6E22C8N — Cyclone 4 примерно 6к ячеек

EP2C8Q208C8N — Cyclone 2 примерно 8к ячеек

Можно заметить, что Cyclone 3 может иметь больше ячеек, чем Cyclone 4.

Вот несколько вариантов:

835 рублей.

ALTERA FPGA CycloneII EP2C5T144 Minimum System Board for Learn good

880 рублей

Altera CycloneII EP2C5T144 FPGA Mini Development Learn Core Board E081

1265 рублей

EP2C8 EP2C8Q208C8N ALTERA Cyclone II FPGA Evaluation Development Core Board

Платы с расширенными возможностями. Это платы, на которых установлены дополнительные модули (UTP, USB, AUDIO), разъемы (SD, VGA), кнопки, переключатели, светодиоды, семисегментные индикаторы и т.д. Либо может идти базовая плата, а к ней могут прилагаться платы расширения отдельно.

Вот основная плата. На ней есть 2 светодиода, 2 кнопки, 4 переключателя, семисегментный интикатор и микросхема оперативной памяти.

Плата расширения. На ней распаяны SD, VGA, а так же контроллеры USB(High Speed USB2.0 Chip: CY7C68013A), AUDIO(Sound Card up to 96kHz/32bit ADC/DAC: WM8731S), UTP(100M Ethernet interface: DM9000A):

Эти платы просто вставляются одна в другую, но у меня она пока лежит в ящике. Для своих поделок у меня макетка, с которой я соединяюсь шлейфом, который идет в комплекте. Еще в комплекте идет блок питания на 5 вольт.

Altera Cyclone NIOS II SOPC FPGA Development Learning Board EP2C8Q208C8N+LCD1602 — 2670 рублей

Terasic Altera FPGA DE0-Nano Cyclone IV Development and Education Board — 4600 рублей

Но в целом, большие и дорогие отладочные платы я бы не рекомендовал сразу покупать. Дорогие покупки должны быть обоснованы, сейчас же пока не ясно что подойдет лучше. Ясно станет, когда начнется практика.

Заказал, ждем

Пока идут платы, можно начать себя морально и технически готовить:

— Установить Quartus II v.11.1

Почитать:

— Книга: А.К. Поляков Языки VHDL и Verilog в проектировании цифровой аппаратуры 2003

— www.kit-e.ru/articles/circuit/2008_3_161.php — Краткий курс HDL

— Уроки на марсоходе по верилогу, архитектура, простые советы по стилю.

— VERILOG как образ жизни

— Хорошие примеры (EN)

— Как начать работать с ПЛИС (Xilinx)

Мы ждем от тебя интересных проектов на ПЛИС!

PS. Обращаясь к тебе на «ты», я обращаюсь, как к равному, личности, а не части толпы. Если обращение на «ты» оскорбило, прошу меня извинить.

ВНИМАНИЕ! Verilog и ПЛИС не являются серебряной пулей и волшебным средством решения любых задач, они не могут заменить микроконтроллеры во всех проектах. Для работы с ПЛИС требуется определенный уровень технической подготовки. Вы сами несете ответственность за все решения в вашей жизни. Автор снимает с себя ответственность за возможные финансовые и временные потери, связанные с вашими исследованиями в области ПЛИС и Verilog.

ПЛИС — мои первые шаги

Как всегда, постижению истин помогло решение реальных задач. В сегодняшней проповеди я хотел бы рассказать об испытаниях, которые выпадают на долю молодого ПЛИСовода. Преодолевая испытания мы постигаем истину. Но остаются вопросы, на которые я не нашел ответов. Поэтому я бы очень хотел, чтобы братья-хабровчане — ПЛИСоводы с опытом, поучаствовали в обсуждении, протянули руку помощи своим младшим собратьям.

Эта статья для новичков. В ней я опишу типичные проблемы, вопросы, заблуждения, ошибки, которые могут появиться в самом начале обучения (потому что они появились у меня). Однако, контекст статьи ограничен тем, что разработка ведется на ПЛИС от Altera в среде Quartus на языке Verilog.

Трудно жить ничего не делая, но мы не боимся трудностей!

Одна из причин, по которой многие не начинают изучать Verilog вот прямо сейчас — это отсутствие реальной ПЛИС. Кто-то не может заказать, потому что дорого, а кто-то потому, что не знает, что именно взять (вопрос выбора рассмотрен в предыдущей статье). Кому-то ПЛИС пока еще едет по почте.

Поэтому мой совет: отсутствие ПЛИС — это не повод бездействовать. Пишите и отлаживайте модули для ПЛИС в симуляторах!

Симулятор для Verilog

Итак, чем же развлечь себя скучными длинными рабочими днями (если они таковыми являются)? Конечно же освоеним ПЛИС! Но как же затащить на работу целую среду разработки от Altera, если она весит 3 ежемесячных рабочих лимита интернета? Можно принести на флешке! Но если предметом изучения является Verilog, то можно ограничиться блокнотом, компилятором IcarusVerilog, а результат смотреть в GTK Wave.

Для начала работы в среде Windows, достаточно скачать по ссылке http://bleyer.org/icarus/ файл установки iverilog-20130827_setup.exe (development snapshot) [11.2MB]

Установка трудностей не вызывает. Теперь немного забежим вперед: создадим папку для проекта и в ней пару файлов с пока что не понятным содержимым:

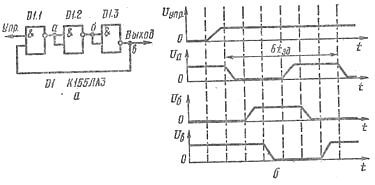

В файле bench.v описан тестовый модуль testbench, в нем создан тестовый источник сигнала clk (меандр). Другие модули будут создаваться в отдельных файлах, либо логику можно протестировать сначала в этом модуле, а потом вынести в отдельный модуль. Потом в модуль testbench будут добавляться экземпляры этих модулей, где мы будем подавать на их входы тестовые сигналы и получать из них результаты. Из модулей мы можем строить иерархию, думаю это понятно всем.

После симуляции наступает пора запуска Quartus. Но загружать прошивку в ПЛИС пока еще рано. Нужно убедиться, что божественная вычислительная машина правильно поняла, какую схему мы хотим получить, изложив свои мысли в виде Verilog’а.

Разница между симуляцией и работой в реальном железе

Первое время я, подобно слепому котенку, бился головой об косяки. Казалось бы правильный код, не работает совсем, либо работает не так, как предполагаешь. Либо вот только что работал, а теперь внезапно перестал!

Пытливый котенок, начинает искать взаимосвязь между своими действиями и результатом («голубиное суеверием»).

Самая большая драма

Ниже будет список странностей, но сначала самая большая драма, с которой я столкнулся: не все конструкции Verilog могут быть синтезированы в железе. Это связано с тем, что на Verilog описывается не только аппаратная логика, которая объединяется в модули и работает в железе. На том же Verilog описываются тестовые модули, которые объединяют тестируемые модули, подают на их входы тестовые сигналы и в целом существуют только для проверки на компьютере. Изменение значений сигналов во времени задается конструкциями, содержащим знак «#» в тексте Verilog. Такой знак означает задержку во времени. В примере выше именно так генерируется сигнал CLK. И я грешным делом думал, что таким же образом внутри настоящей ПЛИС можно генерировать, к примеру, последовательность бит для отправки сообщения по RS232. Ведь на вход ПЛИС подан сигнал от генератора 50 МГц! Может быть она как-то на него ориентируется. Как оказалось, я не единственный, кто надеялся на чудо: 1, 2, 3, 4, 5. Реальность как всегда оказывается более суровой: ПЛИС это набор логики и временная задержка в ней может появиться при использовании счетчика, значение которого увеличивается тактами от генератора до заданной величины, либо как-то иначе (но всегда аппаратно).

Список найденных странностей

Удивительные вещи, однако, прочтение книг [1,2] проливает свет на эту бесовщину. Более того, обретается благодать.

Если обозначить reg, то не факт, что он будет создан

Как я пришел к проблеме? Допустим есть один модуль, на вход которого я должен подавать значение (по типу параметра). В перспективе, этот параметр должен будет изменяться во времени в зависимости от каких-то внешних событий. Поэтому значение должно хранится в регистре (reg). Но реализация приема внешних событий пока не реализована, поэтому я регистр не меняю, а просто задаю ему изначальное значение, которое в дальнейшем не меняется.

Казалось бы в чем подвох? В императивных ЯП мы часто задаем переменные в качестве констант и потом ни разу их не меняем и все работает. Что же мы видим в железе?

Во-первых, мы не видим регистра. Во-вторых, на вход модуля подано 8’hFF вместо наших 8’d0240! И этого уже достаточно для того, чтобы схема заработала не так, как мы планировали. То, что регистра нет — это нормально. В Verilog можно описывать логику разными способами, в то же время, синтезатор всегда оптимизирует аппаратную реализацию. Даже если написать блок always и в нем работать с регистрами, но при этом выходное значение всегда будет определяться входными, то применение регистра тут окажется лишним и синтезатор его не поставит. И наоборот, если при каких то значениях входных данных выходное значение не меняется, то тут никак не обойтись без регистра-защелки и синтезатор его создаст. (Книга 1 стр. 88-89). Что из этого следует? Если мы начнем менять значение регистра, например, в зависимости от нажатии кнопок, то геристр уже будет создан и все будет работать так, как нужно. Если же окажется, что кнопки ничего не меняют, то синтезатор его опять же выкинет и опять все поломается. Что же делать с константой? Нужно подать ее напрямую на вход модуля:

Теперь на входе модуля мы имеем правильное значение:

Остается загадкой, почему при сокращении регистра, его значение в initial не подставляется на вход модуля.

Размерность wire лучше задавать самому.

При разработке в среде Quartus, допускается не задавать линии wire заранее. В этом случае они будут созданы автоматически, но об этом будет выдано предупреждение (warning). Проблема заключается в том, что разрядность wire будет 1-бит, а если порты будут иметь разрядность больше 1 бита, то значение не будет передано.

Результат:

Как видим, один бит подключен, а остальные 7 бит получаются не подключены (NC). Чтобы такой проблемы не было — нужно создать wire самостоятельно. Не зря компилятор IcarusVerilog выдает не warning, а ошибку, если wire не задан заранее.

Компьютер не будет лазать по модулям, смотреть, какая разрядность портов. К тому же, разрядность может оказаться разной, а на вход модуля или с выхода берутся не все биты, а какие-то определенные.

Нельзя использовать выход логической функции, в качестве тактового сигнала

Иногда в проекте требуется снизить тактовую частоту, либо ввести временную задержку в N тактов. Новичёк может применить счетчик и дополнительную схему определения достижения счетчиком определенного значения (схема сравнения). Однако, если напрямую использовать выход со схемы сравнения в качестве тактового, то могут возникнуть проблемы. Это связано с тем, что логической схеме требуется некоторое время для установки стабильного значения на выходе. Эта задержка смещает фронт сигнала, проходящего через разные части логической схемы относительно тактового, в итоге получаются гонки, метастабильность, асинхронщина. Даже довелось однажды услышать реплику об этом в качестве критики ПЛИС: «с ПЛИС постоянные проблемы — гонки сигналов».

то становится ясно, каким образом разрабатываются устройства на ПЛИС: вся задача делится на аппаратные блоки, а данные между ними движутся по конвеерам, синхронно защелкиваясь в регистрах по тактовому сигналу. Таким образом, зная общую тактовую частоту, синтезатор рассчитывает максимальную частоту работы всех комбинаторных схем, определяет, укладывается ли их скорость к период такта и делает вывод — будет или не будет работать схема в ПЛИС. Все это происходит на этапе синтеза. Если схемы укладываются в параметры, то можно прошивать ПЛИС.

Для полного понимания, стоит прочитать Altera handbook на предмет «clock domains», а так же разобраться с тем, как задавать параметры рассчета TimeQuest для проекта.

Таким образом, для разработчиков устройств на базе ПЛИС созданы все необходимые методологии, и если их придерживаться, то проблем не будет.

А что, если я хочу пойти против системы?

Порядок разработки и поведение синтезатора схем подводит нас к выводу о том, что же такое ПЛИС на аппаратном уровне. Это синхронные схемы. Поэтому, среди целей синтезатора — уложиться во временные интервалы. Для этого он, к примеру, упрощает логические выражения, выбрасывает из синтеза части схем, которые не используются другими схемами и не привязаны к физическим выводам ПЛИС. Асинхронные решения и аналоговые трюки не приветствуются, потому что их работа может быть непредсказуемой и зависеть от чего угодно (напряжение, температура, техпроцесс, партия, поколение ПЛИС), а поэтому не дает гарантированного, повторяемого, переносимого результата. А всем же нужен стабильный результат и общие подходы к проектированию!

Но что же делать, если вы не согласны с мнением синтезатора о том, что нужно выкидывать неизменяемые регистры, сокращать логические схемы? Как быть, если хотите делать схемы с асинхронной логикой? Нужна тонкая настройка? А может быть вы сами хотите собрать схему на низкоуровневых компонентах ПЛИС? Легко! Спасибо разработчикам Altera за такую возможность и подробную документацию!

Как это сделать? Можно попробовать графический редактор схем. Вы, возможно, слышали о том, что Quartus позволяет рисовать схемы? Можно самому выбрать стандартные блоки и соединить их. Но это не решение! Даже нарисованная схема будет оптимизирована синтезатором, если на это будет возможность.

В итоге мы приходим к старой истине: если ничего не помогает — прочитайте инструкцию. А именно «Altera Handbook» часть под названием «Quartus II Synthesis Options».

Начнем с того, что описывая архитектуру на Verilog определенным образом, можно получить определенный результат. Вот примеры кода для получения синхронного и асинхронного RS триггера:

В этом случае получится синхронный триггер.

Если не брать во внимание тактовый сигнал и переключаться в зависимости от любых изменений r и s, то в результате получится элемент с асинхронной установной значений — защелка (latch).

Но можно пойти еще дальше и самому создать защелку из примитива (примитивы доступны так же, как любой другой модуль Verilog):

В итоге, весь «обвес» на входе защелки, который синтезатор посчитал ненужным, исчезнет и мы получим именно то, что хотели:

Список существующих примитивов можно посмотреть на сайте Altera.

А теперь небольшой пример про асинхронность и сокращение. Задумал я, к примеру, сделать генератор по тому же принципу, как это было принято делать раньше, но только на ПЛИС:

Но для увеличения периода я возьму 4 элемента, но только один из них будет с инверсией:

Но получается сокращение (1 элемент, вместо четырех). Что логично. Но мы то задумывали линию задержки.

Но если поставить синтезатору условие, что линии a,b,c,d не сокращать, то получится то, что мы задумали. Для подсказки синтезатору применяются директивы. Один из способов указания — это текст в комментарии:

А вот и результат — цепочка из четырех элементов:

И это далеко не все! Оставлю на радость самостоятельного изучения: работу с case и директиву для реализации его в качестве RAM/ROM или логической схемой; работу со встроенными блоками памяти (RAM/ROM); выбор реализации умножения — аппаратным умножителем или логической схемой.

Выводы

Цитируя статью, хочу сказать, что «ПЛИС-ы / FPGA — не процессоры, «программируя» ПЛИС (заполняя конфигурационную память ПЛИС-а) вы создаете электронную схему (хардвер), в то время как при программировании процессора (фиксированного хардвера) вы подсовываете ему цепочку написанных в память последовательных инструкций программы (софтвер)».

Причем, как бы мне изначально не хотелось сильно не привязываться к конкретной железяке, но иногда, чтобы более эффективно и экономно использовать ресурсы, приходится работать на низком уровне. Часто этого можно избежать, если правильно разрабатывать синхронные схемы. Однако совсем забыть, что это железо — не получается.

Еще хочу сказать, что фанатизма и максимализма со временем поубавилось. Сначала я стремился все действия и рассчеты на ПЛИС выполнять за один такт, потому что ПЛИС это позволяет. Однако, это требуется далеко не всегда. Вычислительные ядра софт процессоров мне пока не довелось использовать, однако применение state machines для работы по определенному алгоритму — стало нормой. Вычисления не за 1 такт, временные задержки в несколько тактов из за применения конвееров — это норма.

Книги, которые мне очень помогли

1. В.В. Соловьев — Основы языка проектирования цифровой аппаратуры Verilog. 2014

2. Altera: Quartus II Handbook

3. Altera: Advanced Synthesis Cookbook

4. Altera: Designing with Low-Level Primitives